PLS Programmierbare Logik & Systeme hat die aktuelle Version seiner Universal Debug Engine (UDE) um umfassende Unterstützung für die RISC-V-Architektur erweitert. Damit lassen sich ab sofort auch Softwareprojekte auf dem neuen Automotive RISC-V Prototype von Infineon Technologies mit gewohnter UDE-Funktionalität entwickeln und analysieren.

Der Automotive RISC-V Prototype von Infineon ist ein vollständiges Software Development Kit (SDK), das bereits in der Pre-Silicon-Phase Softwareentwicklung ermöglicht. Es basiert auf einem virtuellen RISC-V-Core-Modell (VP) mit Synopsys VDK-Technologie und beinhaltet neben dem Multicore-RISC-V-Cluster auch typische Automotive-Peripherie, Treiber und ein Projekt-Template für schnelles Prototyping.

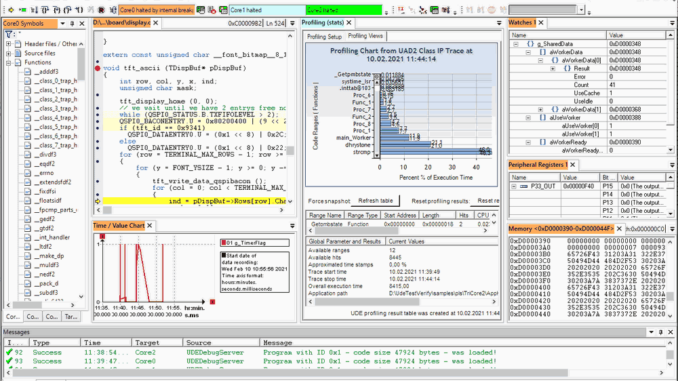

PLS’ Universal Debug Engine (UDE) erkennt den Prototyp als virtuelles Target, bietet jedoch dieselbe Benutzeroberfläche und Funktionalität wie bei echter Hardware. Dazu zählen C/C++- und Assembler-Debugging, Multi-Core-Synchronisation, umfassender Registerzugriff und leistungsstarke Trace-Funktionen. Letztere ermöglichen unter anderem die Visualisierung von Funktionsverläufen, Laufzeitanalyse und Call-Graph-Rekonstruktion. Dank der identischen Bedienung für virtuelles und reales Target erleichtert UDE den nahtlosen Übergang zur späteren RISC-V-Hardware – ohne Toolwechsel. (oe)