Mit dem Projekt Digital Autonomy with RISC-V in Europe, Special Grant Agreement 1 (DARE SGA1) wird offiziell die erste Phase einer Initiative zur Stärkung der technologischen Souveränität Europas im Bereich des Hochleistungsrechnens (HPC) und der künstlichen Intelligenz (KI) eingeleitet.

Das dreijährige Projekt ist Teil der sechsjährigen DARE-Initiative und wurde mit 240 Mio. Euro ausgestattet.

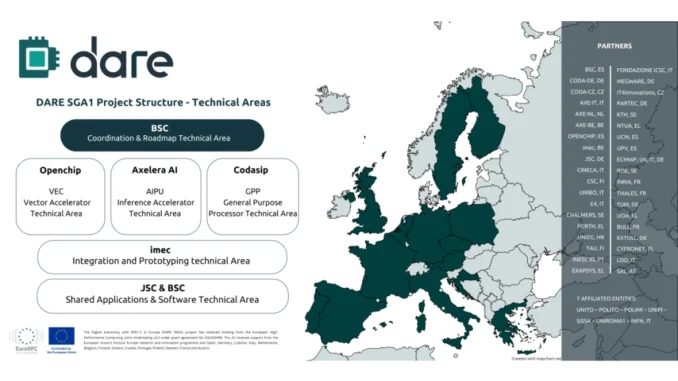

Unterstützt vom gemeinsamen Unternehmen EuroHPC und koordiniert vom Barcelona Supercomputing Center (BSC-CNS), vereint DARE SGA1 38 führende Partner aus ganz Europa, um europäische Prozessoren und Rechensysteme der nächsten Generation zu entwickeln, einschließlich eines optimierten Software-Ökosystems, das für Anwendungen in Forschung und Industrie konzipiert ist.

Das Herzstück des DARE SGA1-Projekts ist die Entwicklung von drei RISC-V-basierten Chiplets, die jeweils eine wichtige Funktion im HPC- und AI-Computing erfüllen:

- Vektor-Beschleuniger (VEC) für Hochpräzisions-HPC und aufkommende Anwendungen im Bereich der HPC-AI-Konvergenz, geleitet von Openchip

- AI Processing Unit (AIPU) für die Beschleunigung von KI-Inferenzen in HPC-Anwendungen, unter der Leitung von Axelera AI

- General-Purpose-Prozessor (GPP) auf RISC-V-Basis, optimiert für HPC-Arbeitslasten in europäischen Supercomputern, unter der Leitung von Codasip

Diese Chiplets werden in fortschrittlichen CMOS-Technologieknoten entwickelt und hergestellt.

DARE SGA1 verfolgt einen HW/SW-Co-Design-Ansatz, dessen Entwicklung auf einer Reihe sorgfältig ausgewählter europäischer HPC- und KI-Anwendungen ausgerichtet ist. Parallel zur HW wir ein kompletter SW-Stack entwickelt, der für die DARE SGA1 HW optimiert ist. Dafür wird ein früher Zugang zu RISC-V HW-Emulation und Simulation genutzt. (jr)