Der Beitrag mit dem Titel „Bis zu 32 Gb/s mit skalierbarer Highspeed-Architektur” stellt die neue Hochgeschwindigkeitsschnittstelle APXpress von Inova für den Automotive-Bereich vor und gibt ein Update zur Silizium-Roadmap.

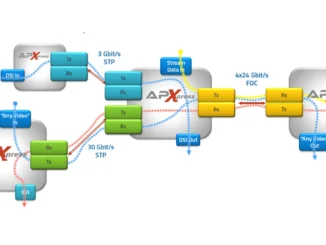

Das konfigurierbare Netzwerk erlaubt eine flexible Zusammenstellung von Knoten, die aus einer Hochgeschwindigkeits-SerDes-Schnittstelle (PHY) und einem prozessunabhängigen IP-Core bestehen. Es unterstützt Datenraten bis zu 32 Gb/s bei variabler Lane-Anzahl.

Nach erfolgreichen FPGA-Demonstrationen steht nun der erste Testchip (T1) zur Verfügung, dessen zentrale Funktionsblöcke – darunter VCO, PLL, digitale Signalverarbeitung und Echo-Cancellation – im Labor validiert wurden.

Das Tapeout für die zweite Iteration (E1) fand Anfang Oktober 2025 statt. Der E1-Chip wird im ersten Quartal 2026 an ein FPGA für weitere Funktionstests und ein PoC angebunden. Das dritte Tapeout (P1) soll ein vollständiges Produkt darstellen und voraussichtlich ab dem zweiten Quartal 2026 direkt in Netzwerken einsetzbar sein. (jr)