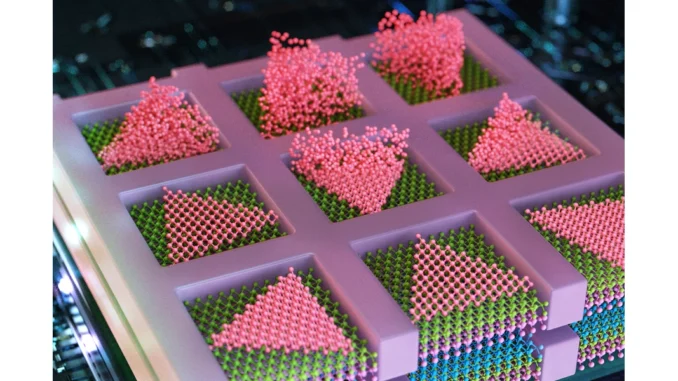

Ein internationales Forscherteam hat eine Methode zum Aufbau mehrschichtiger Chipdesigns auf Basis von Übergangsmetalldichalcogenid (TMD) entwickelt, die ohne Siliziumsubstrat als Zwischenschicht auskommt und bei so niedrigen Temperaturen funktioniert, dass tieferliegende Schaltkreise beim Aufbau der nächsten Schicht nicht wieder zerstört werden.

Die Methode ermöglicht es, Hochleistungstransistoren sowie Speicher- und Logikelemente auf jeder beliebigen kristallinen Oberfläche zu bauen und nicht nur auf Wafern.

Wollen Ingenieure bislang Chips stapeln, musste jeder Chip auf einem Siliziumsubstratboden aufgebaut werden. Dieser Boden behinderte nach dem Stapeln die Kommunikation zwischen den funktionalen Halbleiterschichten. Durch den Wegfall können die Halbleiterschichten in direkterem Kontakt stehen, was zu einer besseren und schnelleren Kommunikation und damit höheren Rechenleistung führt.

Die Forscher erwarten, dass sie so gestapelten Chips für Laptops oder tragbare Geräte bauen können, die so schnell und leistungsfähig wie die heutigen Supercomputer wären und riesige Datenmengen auf dem Niveau physischer Datenzentren speichern könnten. (jr)