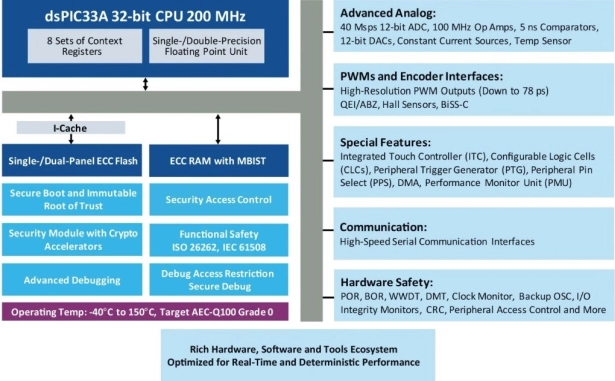

Die neue dsPIC33A-Familie von Microchip nutzt eine 32-Bit-CPU-Architektur mit 200 MHz Taktfrequenz und verfügt über eine Double-Precision Floating-Point-Unit (DP FPU) sowie DSP-Anweisungen für rechenintensive Regelungsaufgaben.

Die Controller bieten eine verbesserte Mathematik und Datenverarbeitung, höhere Code-Effizienz, schnelleren Kontextwechsel und eine reduzierte Latenz.

Die Familie verfügt über neue und verbesserte Peripherie wie speziell für die Motorsteuerung und digital geregelte Leistungswandlung entwickelte hochauflösenden PWMs sowie 12-Bit-A/D-Wandler mit einer Wandlungsrate von bis zu 40 MSamples/s, schnelle Komparatoren und Operationsverstärker. Die Analog-Peripherie ermöglicht zusammen mit CIPs (Core-unabhängiger Peripherie) anspruchsvolle Sensorik und eine leistungsstarke Steuerung. Hinzu kommt Interaktion zwischen der Peripherie, ohne dass die CPU beteiligt sein muss, was die Effizienz eines einzelnen Controllers bei der Verwaltung mehrerer Aufgaben erhöht.

dsPIC33A-DSCs sind mit Flash-Sicherheitsfunktionen ausgestattet, darunter eine unveränderbare Root of Trust, sicheres Debugging und eingeschränkter Speicherzugriff. Die Befehlssatzarchitektur (ISA; Instruction Set Architecture) der DSCs ermöglicht die Übernahme von Software-Code, der durch modellbasierte Designs generiert wurde, um die Code-Erzeugung zu vereinfachen.

Die erste Serie der Familie, die dsPIC33AK128MC1xx-DSCs haben 128 KB Flash und umfassende Peripherie an Bord und sind in verschiedenen Gehäuse-Optionen wie SSOP, VQFN und TQFP erhältlich. Zukünftige dsPIC33A-Serien mit zusätzlichem Speicher, mehr Peripherie und größerer Pinzahl sollen das Angebot vervollständigen. (jr)