Renesas hat einen konfigurierbaren ternären inhaltsadressierbaren Speicher (TCAM) auf Basis eines 3-nm-FinFET-Prozesses vorgestellt. Der neue TCAM bietet eine höhere Dichte, einen geringeren Stromverbrauch und eine verbesserte funktionale Sicherheit.

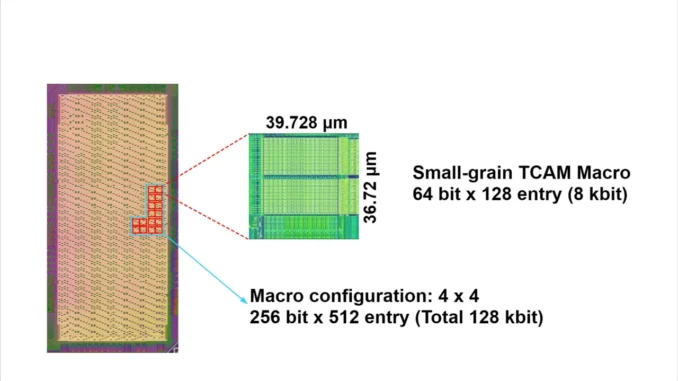

Die neu entwickelten TCAM-Hard-Makros werden von einem Speichercompiler mit feiner Granularität unterstützt. Dieser unterstützt Suchschlüsselbreiten von 8 bis 64 Bit und Eintragstiefen von 32 bis 128.

Größere Konfigurationen (z. B. 256 Bit × 4.096 Einträge) werden durch die Kombination dieser Hard-Makros mit der werkzeuggesteuerten, automatischen Generierung von Soft-Makros realisiert. So wird ein konfigurierbares Einzelmakro bereitgestellt, das eine Vielzahl von Anwendungsfällen auf einem Chip abdeckt. Damit wird eine branchenführende Speicherdichte von 5,27 Mb/mm² erreicht.

Jedes Hard-Makro integriert eine All-Mismatch-Erkennungsschaltung und führt eine zweistufige Pipeline-Suche durch. Basierend auf dem Ergebnis der ersten Stufe kann die zweite Stufe fortgesetzt oder angehalten werden, um unnötigen Energieverbrauch zu vermeiden. Bei Konfigurationen mit 64–256 Bit × 512 Einträgen reduziert dieser Ansatz den Suchenergieverbrauch beispielsweise um bis zu 71,1 % bei einer spaltenweisen Pipeline-Suche (mit Schlüsselpartitionierung, >64-Bit-Schlüssel) und um bis zu 65,3 % bei einer zeilenweisen Pipeline-Suche (ohne Schlüsselpartitionierung, ≤64-Bit-Schlüssel).

In einer Konfiguration mit 256 Bit × 512 Einträgen erreicht das Design einen energiesparenden Betrieb mit einer Suchenergie von 0,167 fJ/Bit und die verteilte Timing-Last ermöglicht einen Such-Takt von 1,7 GHz. Die resultierende TCAM-Leistungszahl (Dichte × Geschwindigkeit ÷ Energie) erreicht 53,8 und übertrifft damit frühere Arbeiten.

Da TCAM-Bitzellen für dieselbe Adresse physisch benachbart sind, kann ein durch einen Soft-Fehler verursachter Doppelbitfehler nicht durch herkömmliches SECDED ECC korrigiert werden. Renesas nutzt zwei Techniken, um dies abzumildern:

Einerseits wird der Datenbus für Benutzerdaten und ECC-Parität in gerade und ungerade Busse aufgeteilt, um die physische Trennung zwischen den Speicherzellen zu vergrößern und potenzielle Doppelbitfehler in korrigierbare Einzelbitfehler umzuwandeln.

Andererseits kommt spezielles SRAM für ECC-Parität mit einem vom TCAM unabhängigen Adressdecoder zum Einsatz, wodurch sich die Erkennbarkeit verbessert, wenn während des Schreibvorgangs im TCAM eine falsche Adresse ausgewählt wird. (jr)