Nach der kürzlichen Eröffnung des gemeinsamen ASML-imec High NA EUV Lithographie-Labors in Veldhoven, Niederlande, haben Kunden nun Zugang zum High NA EUV-Scanner, um Design nach den eigenen Designregeln und Layouts zu entwerfen.

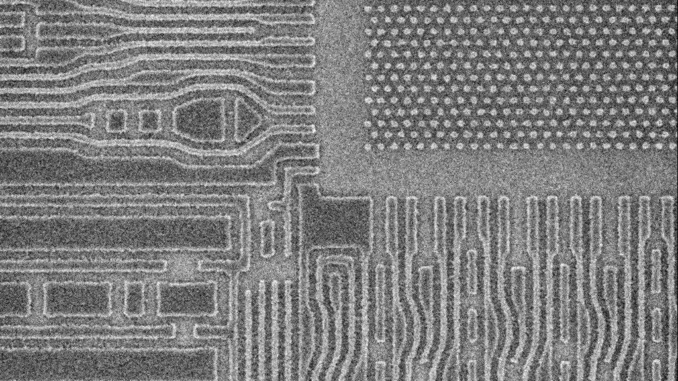

Imec hat erfolgreich Random-Logic-Strukturen in Einzelbelichtung mit nur 9,5 nm breiten Metallbahnen strukturiert, was einem Pitch von 19 nm entspricht, und dabei Tip-to-Tip-Abmessungen von unter 20 nm erreicht. Random Vias mit einem Abstand von 30 nm von Mittelpunkt zu Mittelpunkt zeigten eine hervorragende Mustertreue und Gleichmäßigkeit der kritischen Abmessungen. Darüber konnten 2D-Strukturen mit einem P22nm Pitch erzeugt werden, was das Potenzial der Hoch-NA-Lithographie für das 2D-Routing verdeutlicht.

Neben logischen Strukturen gelang es Imec, in einer einzigen Belichtung Designs zu strukturieren, die das Landing Pad des Speicherknotens mit der Bit-Line-Peripherie für DRAM integrieren. Diese Errungenschaft unterstreicht das Potenzial der High-NA-Technologie, die mehrere Maskenschichten durch eine einzige Belichtung ersetzen kann. (jr)