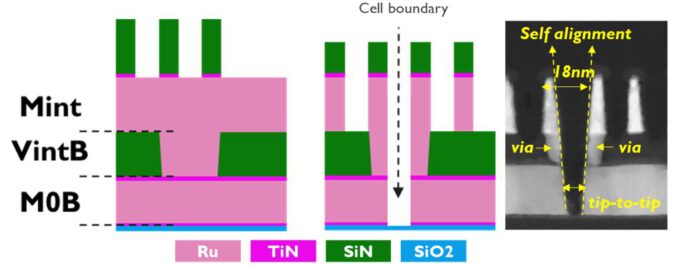

Imec, das Forschungs- und Innovationszentrum für Nanoelektronik und digitale Technologien hat einen Semi-Damascene-Integrationsansatz zur Implementierung des vertikal-horizontal-vertikalen (VHV) Skalierungsboosters vorgestellt, der 4-Spur-Standardzellen (4T) ermöglichen soll. Der Prozess ermöglicht eine Skalierung der Zellgrenzen auf bis zu 8 nm Tip-to-Tip in den MOL-Schichten und bietet selbstausrichtende Kanten. Designer können mit diesem Booster Standardzellen dichter packen und damit gegenüber 5T-Designs 21% Platz einsparen. Das neuartige Routing-Schema soll es zusammen mit der Semi-Damascene-Integration ermöglichen, die Logik-Roadmap schrittweise bis weit in die Å-Ära zu verlängern.

Link zur Meldung