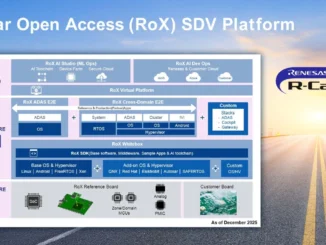

Renesas hat drei SoC-Techniken entwickelt, die die Integration mehrerer Domänen auf einem Steuergerät (ECU) vereinfachen. Erste Anwendungen finden die Techniken in den neuen Automotive-SoCs der R-Car-X5H-Serie.

Die nunvorgestellten Techniken gewährleisten für die erforderliche Rechenleistung, Skalierbarkeit und funktionale Sicherheit, die für den Einsatz in softwaredefinierten Fahrzeugen (SDVs) mit moderner E/E-Architektur unerlässlich sind. Gleichzeitig verbessern sie die erreichbare Qualität und Energieeffizienz der SoCs.

Die drei Weiterentwicklungen im Einzelnen:

Neue Chiplet-Architektur für ASIL-D-Anwendungen

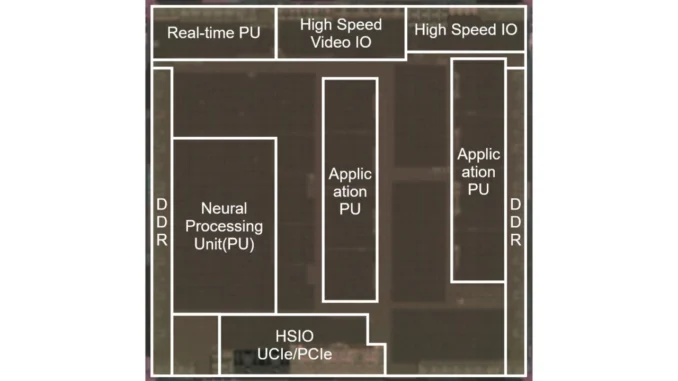

Um die Anforderungen an die funktionale Sicherheit von Automobil-SoCs zu erfüllen, hat Renesas eine neue, proprietäre Architektur entwickelt, die ASIL D auch in einer Chiplet-Konfiguration unterstützt. Durch die Kombination der standardmäßigen Die-to-Die-UCIe-Schnittstelle mit einem proprietären RegionID-Mechanismus verhindert die Architektur Interferenzen mit Hardware-Ressourcen, selbst wenn zahlreiche Anwendungen gleichzeitig ausgeführt werden. Auf dieser Weise wird Interferenzfreiheit (FFI) erreicht.

Herkömmlichen UCIe-Schnittstellen fehlt die Funktionalität zur Übertragung von RegionIDs zwischen Dies. Renesas hat eine Methode entwickelt, mit der sich RegionIDs in den physischen Adressraum abbilden, in den UCIe-Bereich codieren und übertragen lassen. Dadurch ist eine sichere Zugriffskontrolle über die Speicherverwaltungseinheit (MMU) und Echtzeit-Kerne möglich, was die Anforderungen an die funktionale Sicherheit über Chiplets hinweg erfüllt. Darüber hinaus wurde durch Tests bestätigt, dass die UCIe-Schnittstelle durch die Aufrechterhaltung der Bandbreite zwischen Prozessoren und Speicherbus eine Übertragungsgeschwindigkeit von 51,2 GB/s erreicht. Damit nähert sie sich der Obergrenze der Übertragungsgeschwindigkeiten innerhalb des SoCs.

Fortschrittliche KI-Verarbeitungsfunktionen und Qualität in Automobilklasse

Renesas hat ein 3-nm-SoC-Design entwickelt, das die Leistung von neuronalen Verarbeitungseinheiten (NPUs) für die KI-Verarbeitung verbessert und gleichzeitig die Qualität der Automobilklasse beibehält. In den letzten Jahren sind NPUs immer größer geworden, ihre Fläche ist im Vergleich zu früheren Generationen um das 1,5-fache gewachsen. Dies hat zu einer erhöhten Taktlatenz zwischen gemeinsamen Taktquellen und einzelnen Schaltkreisen geführt. Um dieses Problem zu beheben, hat Renesas die Taktarchitektur neu gestaltet: Die Taktimpulsgeneratoren (CPGs), die in früheren Designs Einheiten auf Modulebene waren, wurden aufgeteilt und als Mini-CPGs (mCPGs) auf Submodul-Ebene platziert. Dies reduziert die Taktlatenz erheblich und erfüllt die Timing-Anforderungen.

Allerdings erschweren mehrschichtige mCPGs die Test-Taktsynchronisation, die für die Erreichung von Null-Fehler-Toleranz in Automobilanwendungen entscheidend ist. Renesas hat daher Testschaltungen in die hierarchische CPG-Architektur integriert und den Signalweg für Benutzer- und Test-Takte vereinheitlicht. Das neue Design synchronisiert außerdem mCPGs der oberen und unteren Ebene unter einer einzigen Taktquelle im Testmodus. Dadurch ist eine einheitliche Phasenanpassung möglich.

Fortschrittliche Leistungssteuerung und -überwachung für verbesserte Energieeffizienz und Sicherheit

Um das für Automobil-SoCs erforderliche hohe Leistungsniveau bei verbesserter Energieeffizienz und Sicherheit zu erreichen, hat Renesas eine fortschrittliche Power-Gating-Technologie mit über 90 Leistungsdomänen entwickelt. Sie ermöglicht eine präzise Leistungssteuerung von wenigen Milliwatt bis zu mehreren zehn Watt, je nach Betriebsbedingungen. Darüber hinaus hat Renesas die Leistungsschalter (PSWs) in Ring-PSWs und Reihen-PSWs unterteilt, um Spannungsabfälle (IR-Drop) zu reduzieren, die mit der zunehmenden Stromdichte aufgrund kleinerer Prozessgeometrien einhergehen. Beim Einschalten unterdrückt der Ring-PSW die Einschaltströme. Anschließend gleicht der Reihen-PSW die Impedanz innerhalb der Domäne aus. Durch diese beiden Maßnahmen werden die IR-Abfälle um etwa 13 % reduziert.

Um die funktionalen Sicherheitsstandards nach ASIL D zu erfüllen, steuert die Dual-Core-Lock-Step-Konfiguration (DCLS) die Master- und Checker-Kerne mit unabhängigen Leistungsschaltern und Controllern. Mit diesem Design kann selbst bei Ausfall einer Seite der Fehler durch den Lock-Step-Betrieb erkannt werden. Darüber hinaus wird für jedes Gate-Signal des PSW eine Loopback-Überwachung durchgeführt, sodass bei Auftreten eines Fehlers der ausgeschaltete Zustand erkannt wird. Für die Spannungsüberwachung wird ein digitales Spannungsmessgerät (DVMON) verwendet, das sehr widerstandsfähig gegen Temperaturdrift ist. Dies verbessert die Alterungstoleranz um 1,4 mV. (jr)