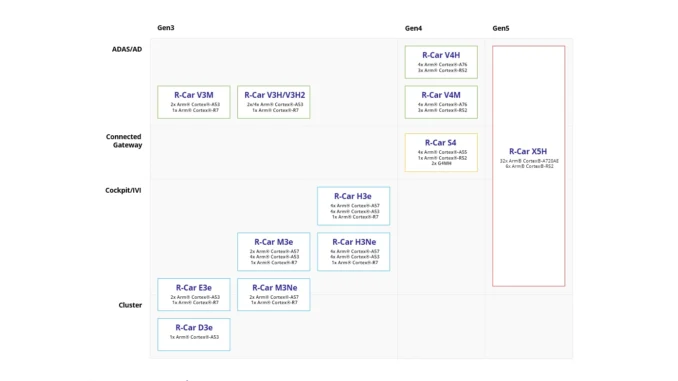

Der erste Baustein der fünften Generation der R-Car-SoC-Familie von Renesas, das R-Car X5H SoC, basiert auf dem neuesten 3-nm-Prozess für die Automobilindustrie und bietet dank seiner hardwarebasierten Isolationstechnologie hochintegrierte, sichere Verarbeitungslösungen für mehrere Automotive-Domänen auf einem einzelnen Chip. Darüber hinaus zeichnet sich das neue SoC durch die Möglichkeit aus, die KI- und Grafikverarbeitungsleistung mittels Chiplet-Technologie zu erhöhen.

Als erster und leistungsstärkster Baustein der fünften Generation (Gen 5) der R-Car-Familie ist der R-Car X5H direkt auf die wachsende Komplexität in der Entwicklung von Software-Defined-Vehicles (SDV) ausgerichtet. Zu diesen Herausforderungen gehören die Optimierung von Rechenleistung, Leistungsaufnahme, Kosten sowie Hardware- und Software-Integration – bei gleichzeitiger Gewährleistung der Fahrzeugsicherheit. Durch die enge Verknüpfung von Anwendungsverarbeitung, Echtzeitverarbeitung, GPU- und KI-Rechenleistung, großen Displays und Sensoranbindung auf einem einzelnen Chip ermöglichen diese Produkte eine neue Klasse von Anwendungen für automatisiertes Fahren, IVI und Gateway.

Die neue SoC-Serie erreicht eine KI-Beschleunigung von bis zu 400 TOPS mit einer branchenführenden TOPS/W-Performance sowie eine GPU-Performance von bis zu 4 TFLOPS. Sie umfasst insgesamt 32 Arm Cortex-A720AE-CPU-Kerne für die Anwendungsverarbeitung. Diese liefern eine Leistung von über 1 Mio. DMIPS. Sechs Arm Cortex-R52 Dual-Lockstep-CPU-Kerne erzielen eine Leistung von über 60k DMIPS und unterstützen ASIL-D-Funktionen ohne externe Mikrocontroller (MCUs). Die neue SoC-Serie wird in einem der fortschrittlichsten Prozessknoten von TSMC gefertigt. Sie erreicht eine erstklassige CPU-Leistung und senkt die Leistungsaufnahme um 30 bis 35 Prozent im Vergleich zu Bausteinen, die für einen 5-nm-Prozessknoten entwickelt wurden. Diese energieeffizienten Merkmale senken die Gesamtsystemkosten erheblich, da keine zusätzlichen Kühllösungen erforderlich sind, und erhöhen gleichzeitig die Reichweite des Fahrzeugs.

Der R-Car X5H nutzt die standardmäßige Die-to-Die-Verbindung UCle (Universal Chiplet Interconnect Express) und APIs für eine nahtlose Chiplet-Integration. Dies erleichtert die Interoperabilität mit anderen Komponenten in einem Multi-Die-System, selbst wenn es sich dabei nicht um Chips von Renesas handelt.

Das R-Car X5H SoC verfügt über hardwarebasierte FFI-Technologie (Freedom from Interference). Diese Hardware-Implementierung trennt sicherheitskritische Funktionen, wie z. B. Brake-by-Wire, von unkritischen Funktionen. Als sicherheitskritisch eingestufte Funktionen lassen sich eigenen redundanten Domänen zuweisen, die jeweils über einen eigenen unabhängigen CPU-Kern, Speicher und eigene Schnittstellen verfügen. Der R-Car X5H verfügt außerdem über ein QoS-Management (Quality-of-Service), das die Prioritäten der Rechenlast bestimmt und die notwendigen Verarbeitungsressourcen in Echtzeit zuweist.

Muster des R-Car X5H werden im ersten Halbjahr 2025 an ausgewählte Automotive-Kunden ausgeliefert. Die Serienproduktion ist für das zweite Halbjahr 2027 geplant. (jr)