Arm hat sein Automotive-Portfolio um eine brandneue Neoverse-CPU der Server-Klasse mit speziell für den Automobilmarkt entwickelten Funktionen, zwei neue Armv9-CPUs der A-Klasse, eine neue CPU der R-Klasse und einen neuen Image Signal Processor (ISP) erweitert. Das Portfolio bietet auch wichtige System-IP, einschließlich Interconnect, Generic Interrupt Controller (GIC) und Memory Management Unit (MMU) für eine breite Palette an SoC-Lösungen.

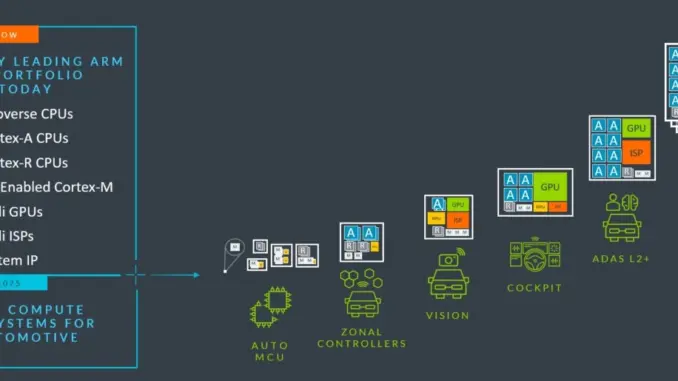

Sie sollen es Anwendern aus der Chipindustrie erleichtern, eine große Bandbreite an Lösungen – die von Zonensteuerungen über digitale Cockpits und Infotainmentsysteme in Fahrzeugen (IVI) bis hin zu fortschrittlichen Fahrerassistenzsystemen (ADAS) und autonomem Fahren reichen – zu entwickeln.

Zusätzlich zu den neuen Prozessoren hat Arm Investitionen in eine Roadmap von Arm Compute Subsystems (CSS) für Automobildesigns angekündigt.

Zur Unterstützung der neuen Arm AE IP kündigen Arm und seine Partner eine Reihe von virtuellen Plattformen an, von denen einige schon verfügbar sind und die für spezifische Fahrzeugfunktionen ausgelegt sind. Hinzu kommen Full-Stack-Softwarelösungen von einer Vielzahl von Partnern aus der Automobilindustrie für eine Vielzahl von SDV-Anwendungen.

Arm Neoverse V3AE wurde für Anwendungsfälle wie High-End-ADAS und autonomes Fahren entwickelt, die höchste Single-Thread-Leistung erfordern. Die CPU verfügt über AE-Funktionen wie Transient Fault Protection (TFP), um den Einsatz in Anwendungen zu ermöglichen, die auf funktionale Sicherheit abzielen. Neoverse V3AE verwendet dieselbe CPU-Leistung und ISA, die auch in den neuesten Cloud- und Rechenzentrumsdesigns eingesetzt wird, um den wachsenden Rechenanforderungen in Fahrzeugen gerecht zu werden.

Außerdem bringen wir zwei neue Arm AE A-Class-CPUs auf den Markt, die sich durch unterschiedliche Leistungs- und Stromverbrauchskompromisse für eine Vielzahl von SDV-Anwendungsfällen auszeichnen. Die A-Class-CPUs und Neoverse V3AE basieren auf der Armv9-A-Architektur.

Der Arm Cortex-A720AE zielt auf Anwendungsfälle wie ADAS, Digital Cockpit und IVI ab, die ein Gleichgewicht zwischen höherer Leistung und verbesserter Energieeffizienz erfordern. Arm hat den Cortex-A720 CPU-Kern um AE-Funktionen wie verbessertem Split-Lock, optionalem TFP und verbesserten Software-Testbibliotheken (STLs) ergänzt.

Der Hersteller gibt an, bei Rechenaufgaben wie der Transformation von Punktwolken und Aufbau einer Vogelperspektivenansicht bei gleicher Leistungsaufnahme eine Performanceverbesserung von 30 % beim Wechsel vom Vorgängermodell Cortex-A78AE zum Cortex-A720AE beobachtet zu haben.

Der Arm Cortex-A520AE zielt auf eine Vielzahl von Anwendungsfällen im Automobilbereich ab, bei denen es zunehmend darauf ankommt, Rechenlasten so effizient wie möglich zu verarbeiten.

Die Kombination von Cortex-A720AE mit Cortex-A520AE in CPU-Cluster-Konfigurationen durch eine neue AE-Version von Arm’s DynamIQ Shared Unit (DSU-120AE) ermöglicht ein breiteres Spektrum an flexibleren, skalierbaren heterogenen SoC-Designs mit bis zu 14 Kerne in einem Cluster.

Der Arm Cortex-R82AE bietet erstmals 64-Bit-Computing für die Echtzeitverarbeitung von Sicherheitsfunktionen. Dieser Echtzeit-Core ermöglicht leistungsfähigere Sicherheitsinseldesigns, die sich nahtlos in den 64-Bit-Speicherbereich integrieren und mit Anwendungsprozessorkernen interagieren. Er unterstützt auch herkömmliche Echtzeit-Computing-Anwendungsfälle und einige umfangreiche Betriebssystem-Workloads (OS).

Der ISP Arm Mali-C720AE unterstützt mehrere parallele Pipelines, die sowohl für Human Vision als auch für CV-Anwendungsfälle unterschiedlich eingestellt werden können. Dadurch wird die für die Bildverarbeitung benötigte Zeit reduziert und die Reaktionszeit des Computersystems insgesamt beschleunigt. Diese mehrfachen ISP-Pipelines reduzieren auch die Speichernutzung, was wiederum Energie und Fläche des SoC spart.

Detaillierte Infos, auch zu den Coherent Mesh Network-IP (CMN S3AE), Generic Interrupt Controller (GIC) GIC-720AE und Memory Management Unit (MMU), Network on Chip (NoC) NI-710AE finden sich in der Originalmeldung. (jr)