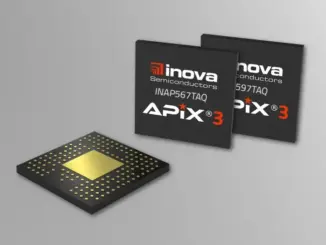

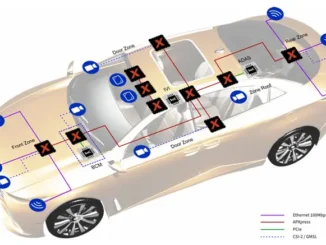

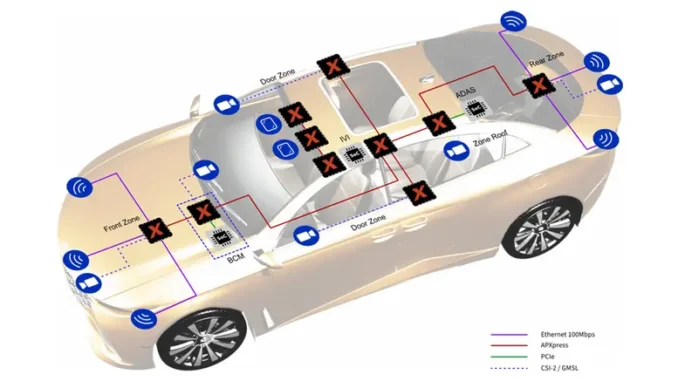

Inova Semiconductors introduces APXpress, a new transmission technology developed for modern vehicle networks with high requirements for bandwidth, latency, and determinism. The architecture is designed to process the increasing amount of data in zonal and software-defined vehicle architectures and to efficiently merge different communication streams via a serial connection.

APXpress enables data rates of 4 to 32 Gbit/s per link and offers a scalable structure with up to 500 independent virtual data paths, allowing flexible bandwidth allocation. Transmission is based on a hardware-implemented SerDes PHY in a 22 nm FDX process. The IP core itself is designed to be independent of specific manufacturing technologies, allowing implementation at different foundries. The technology supports both copper-based and optical lines and can be operated in full-duplex or dual-simplex mode.

Mechanisms such as FEC error correction and redundant cell transmission are integrated to ensure data integrity and system reliability. This makes APXpress suitable for applications with high security and availability requirements, such as camera systems, radar sensors, infotainment, or as a communication infrastructure for zonal control units. Deterministic execution and defined latency address key challenges in software-defined architectures where heterogeneous data streams must be processed in parallel.

Following successful FPGA demonstrations, the first test chip (T1) is now available, with its central functional blocks—including VCO, PLL, digital signal processing, and echo cancellation—validated in the laboratory. The tapeout for the second iteration (E1) took place in early October 2025. The E1 chip will be connected to an FPGA in the first quarter of 2026 for further functional testing and a PoC. The third tapeout (P1) is intended to represent a complete product and is expected to be ready for direct use in networks from the second quarter of 2026. (oe)

Further information (white paper and product sheet)